Projects:2018s1-136UG Rate of Change of Mains Frequency Detection

Abstract

The Rate of Change of Frequency (ROCOF) detection of mains voltages is very important to maintain a stable electricity supply. The present IEEE standard for ROCOF detection involves converting the mains voltages to phasors and using those to determine the ROCOF. Normally with 100 times per second updates.

C.J. Kikkert has developed a new algorithm for detecting magnitude and phase directly from the voltage waveforms, without phasor conversion or filtering. That algorithm needs some further development to accurately calculate Frequency and ROCOF with low delay and low sample to sample variations. The waveform recorders used typically have a 9.6 kSPS data rate. The new algorithm produces frequency and ROCOF values at that 9.6 kSPS data rate, so that there is less delay in detecting any disturbance.

The project involves firstly optimising the algorithm to ensure the ROCOF information provided is the best fit for the purpose of maintaining power system stability.

The next and biggest part is developing Verilog or VHDL code for implementing this algorithm into an FPGA and implementing that in hardware. (Possibly using a commercially available FPGA development board with ADC’s added).

This should then result in hardware that provides mains frequency and ROCOF information.

Front end structure

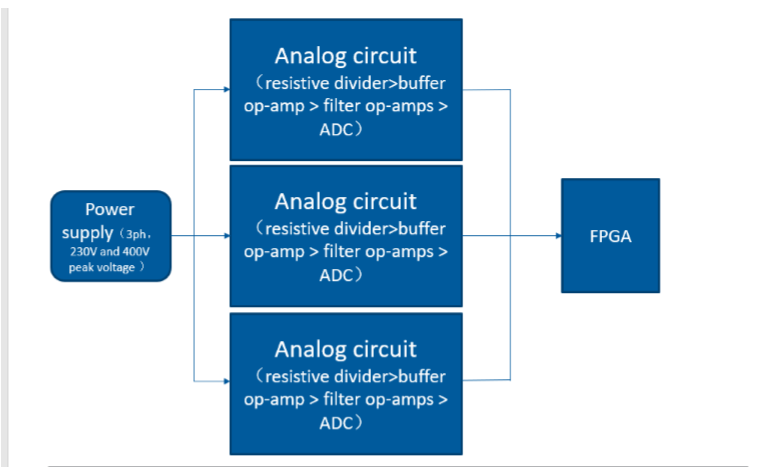

The reason why we decided to make a PMU to process the original 3 phase 240V AC mains input is that voltage level was too high for algorithm analysis environment(ADC and FPGA).The main front end structure as show as below.

There are the main relate knowledge of the PMU design:Operational Amplifier;Sallen-key Bessel anti-alias filter;Flash testing.

Team Members

- Nathan Reid

- Wenkang Li

Supervisors

- Keith Kikkert

- Said Al-Sarawi