Projects:2015s1-18 ARM Processor For Digital Systems Practicals

ARM processors collectively forms a family of CPUs. These processors are developed by Advanced RISC machines. ARM processors are based on reduced instruction set computer (RISC). Today, ARM processors are widely used, across different applications, such as in iPhone, tablets and e-readers.

In this project, we were required to design an ARM processor, called disARMed. The disARMed processor is simple, easy to understand, and follows the ARM architecture.

Contents

Introduction

Aim

The aim of the project is to aid first year and second year students with their learning of digital systems and computer architecture in Digital Systems courses. The outcome of the project is to create a set of tools as a teaching aid for the laboratories of these Digital Systems courses.

Motivation

The project is being undertaken for the following reasons:

1. The University of Adelaide is restructuring the degrees under the School of Electrical and Electronics Engineering. There will be brand new Digital Systems courses available for the first and second year students under the School of Electrical and Electronics Engineering. A teaching aid is required for the practicals of these courses.

2. These courses uses the Digital Design and Computer Architecture textbook as its primary textbook resource and a new edition of it, which is the ARM edition, will be published this year, on the 1st of May 2015.

The ARM Processor for Digital Systems Practicals project is desired by the lecturers and practical organizers of the Digital Systems courses. The students of these courses will use the products of the project, in their practicals, for a better understanding of Digital Systems and Computer Architecture such as being able to relate the static nature of the instruction mnemonic to the dynamic nature of its execution. The lecturers will maintain, modify and extend the product to suit the specific practical exercises they will make for the courses.

Use Case Scenarios

This section describes the scenarios of how and where the teaching aid will be used.

1st Year Digital System course laboratories

Students will be provided with an example assembly language program. They will simulate the program on the Host PC and observe the execution of the instructions. They can modify the program.

The students will run the example assembly language program on the FPGA board and observe the outcome. There will be specifications provided in the lab which require the students to design logic blocks to connect the disARMed processor with the peripheral blocks such as the LEDs.

Figure 1.2 shows an example where the students are required to connect the disARMed microprocessor with the LEDs peripheral block with the address decoder coloured in blue.

2nd Year Digital System course laboratories

Second year students will create their own assembly language programs and simulate it on the Host PC. They will observe how each instruction is executed, the datapath each instruction follows, and the change in values in the registers and memory.

The students will download their assembly program onto the Basys-2 FPGA board and run it with the disARMed microprocessor. They will observe the interactions of the microprocessor with the peripheral blocks on board the Basys-2 FPGA board.

In addition, students will explore the Verilog code of the disARMed microprocessor. Students will be given an incomplete disARMed microprocessor where they have to design and implement the missing module.

For example, the microprocessor may be missing the ALU component and students will be required to design their own ALU as shown below (in blue rectangle).

Key Requirements

- Design an ARM processor called disARMed. The architecture for the disARMed processor is provided in the next session.

- Implement a system to allow Host PC to communicate with and control the disARMed processoe.

- Implement a system to simulate a disARMed processor.

- Implement a system for converting disARMed assembly program to machine code.

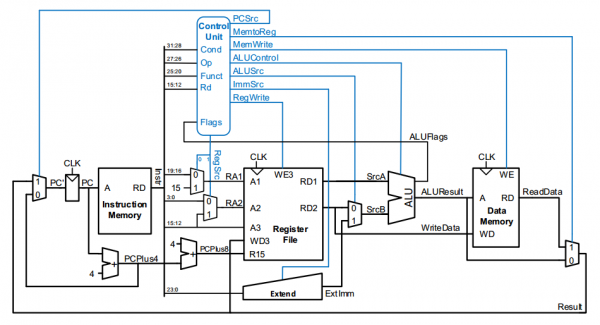

disARMed Processor Architecture

The disARMed processor is a simple 32 bit ARM processor.

It is/has:

- Single cycle: only one instruction is executed in each cycle.

- No pipe-lining: instructions are executed one at a time.

- Small set of registers: there are only 16 registers, r0 – r15.

- Simple instruction set: The instruction set only contains load/store instructions, data processing instructions and branch instructions.

It also has the following general features of ARM architecture

- A load and store architecture, where data processing operates only on register contents and not directly on memory contents [1].

- Simple addressing modes, where all load and store addresses are determined from the instruction fields and contents of registers [2].

- Fixed length instruction fields [1]

- Automatic increment addressing modes. These modes are used for optimizing program loops [2].

- Conditional execution of almost all instructions in the instruction set. This is to maximize execution throughput [2].

- Control over Arithmetic Logic Unit (ALU) in data-processing instructions for maximizing the usage of the ALU [2].

System Overview

In this section, we will discuss how the system works.

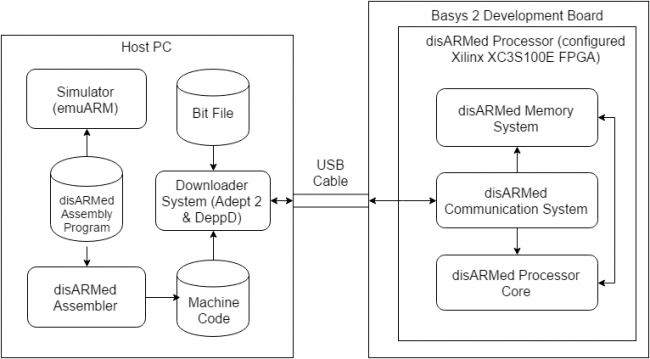

System Design

The following diagram shows the overview of the system, as well as how information will flow within the system.

disARMed Processor

Processor Core

The core of the processor is responsible for executing instructions. It is capable of retrieving instructions from the instruction memory, decipher the type of instruction and execute it accordingly. It is also able to store and retrieve data from the data memory.

Memory System

The memory system is the collection of memories required by the disARMed processor. It is used for storing the information required by the disARMed processer core. The memory system is composed of the following memories: data memory, instruction memory and memory for IO devices.

- The data memory stores data.

- The instruction memory holds the list of instructions to be executed by the processor

- The IO memory are registers connected to the IO devices such as LEDs and Seven Segment Display.

Communication Interface

The communication interface is required for receiving information from the Host PC. It performs the following functions:

- Retrieve information from Host PC.

- Decipher the type of information received.

- If control signal is received, forward it to the appropriate system of the disARMed processor.

- If instruction is received, store it into instruction memory.

Downloader System

The purpose of the downloader is to upload the bit file and the machine code file onto the Basys-2 FPGA board. The downloader will upload the bit file onto the FPGA board first before uploading the machine code containing the instructions to be executed.

DeppD

DeppD is an application designed for sending machine code to the disARMed processor. It was created in Java such that it can be used in Windows and Linux operating system. As shown in Figure 5 there are two buttons for use: reset & send. Reset need to be finished to initialize Basys2 board before the machine code can be sent.

Adept 2

The Adept 2 application is a PC interface developed by Digilent Inc. This interface is used with Digilent’s programmable board such as the Basys 2. It can be used for configuring the Digilent devices, download and upload data files to and from the device, expand the I/O capability and run tests to confirm the device is operating correctly [3].

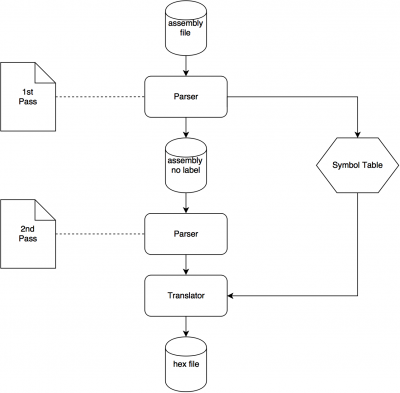

disARMed Assembler

Assembler is the program that reads the disARMed assembly code and translates it to machine code. The assembler has two main modules, parser and translator. Parser breaks each assembly instruction into its underlying components (operators and operands and other fields), and translator generates machine code(hex code), according to encoding rules.

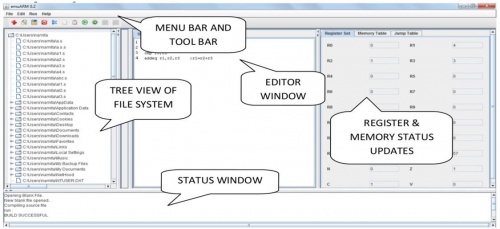

emuARM

The emuARM is an existing open-source ARM instruction set emulator written in java, it reads in assembly code and emulates the behavior of an ARMv5 microprocessor. As can be seen below is the software GUI, users can edit assembly code in emuARM and run it to see the effect on changing registers and memory values. The purpose of the emuARM is to simulate the disARMed processor and executes the instructions, allowing the user to visually observe what is occurring, and if the program is working correctly, as desired. For more information see [4].

Project Outcomes

The disARMed processor has been designed. It is currently in the final stages of system testing. A basic downloader system and assembler have been created. The emuARM simulator have been incorporated into the teaching aid.

Conclusion & Further Work

Most of the requirements of the system has been achieved. Further work will be required to meet the remaining requirements of the project. These are:

- Integrating the downloader, assembler and simulator into a single system.

- Complete system testing of the disARMed processor.

References

[1] Arm.com, 'ARM Processor Architecture - ARM', 2015. [Online]. Available: http://www.arm.com/products/processors/instruction-set-architectures/index.php. [Accessed: 28- May- 2015].

[2] ARM Architecture Reference Manual, 1st ed. ARM Limited, 2015.

[3] Adept Application User’s Manual, Digilent, WA, 2010, pg. 1-2.

[4] Malhotra, G.; Atri, N.; Sarangi, S.R., "emuARM: A tool for teaching the ARM assembly language," in e-Learning and e-Technologies in Education (ICEEE), 2013 Second International Conference on , vol., no., pp.115-120, 23-25 Sept. 2013